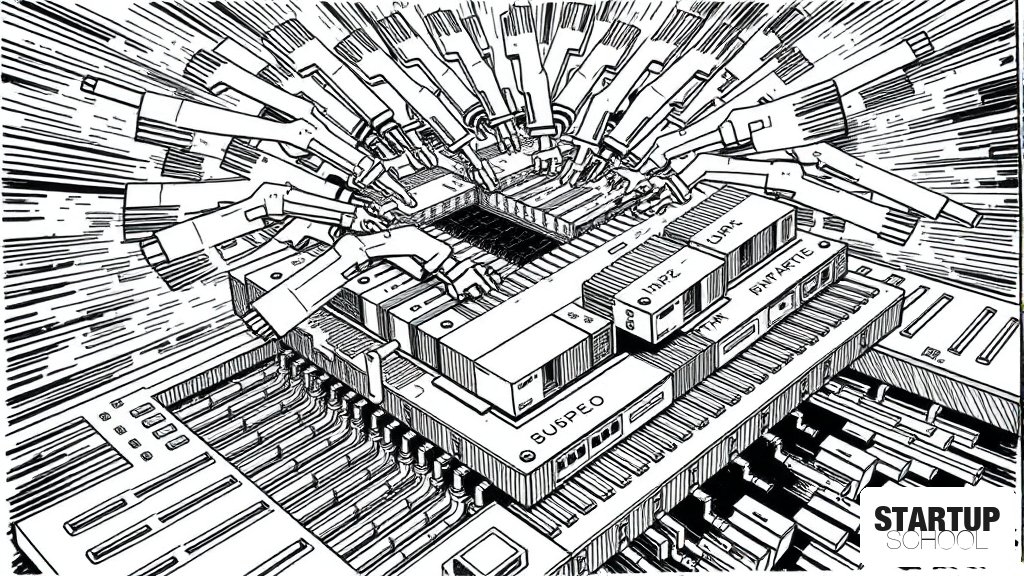

80386 메모리 파이프라인

(nand2mario.github.io)

FPGA로 구현된 80386 코어가 복잡한 가상 메모리 관리 프로세스를 어떻게 1.5 클럭이라는 놀라운 속도로 처리하는지, 그 핵심인 메모리 파이프라인의 최적화 원리를 분석합니다. 단순한 직렬 구조를 넘어 파이프라이닝과 병렬 처리를 통해 지연 시간을 최소한으로 줄인 마이크로아키텍처의 정수를 다룹니다.

- 1FPGA 기반 803나 386 코어가 75MHz에서 DOS 및 Doom 실행 가능함을 증명

- 2가상 메모리 주소 변환 과정을 1.5 클럭 내에 완료하는 파이프라인 최적화 기술

- 3세그먼트 변환과 페이지 변환을 직렬이 아닌 병렬 및 오버랩 구조로 설계

- 4마이크로코드를 통한 RD(Read) 및 DLY(Delay) 훅을 활용한 메모리 접근 제어

- 5연속된 명령어 실행 시 발생하는 주소 생성 지연을 최소화하는 하드웨어 반응성

왜 중요한가

배경과 맥락

업계 영향

한국 시장 시사점

이 글은 기술적 복잡성을 마주한 엔지니어와 창업자들에게 '복잡성을 관리하는 방법'에 대한 강력한 통찰을 제공합니다. 80386의 사례처럼, 새로운 기능(32비트 보호 모드)을 도입할 때 발생하는 성능 손실을 단순한 하드웨어 성능 향상이 아닌, 구조적 혁신(파이프라이닝 및 병렬화)을 통해 해결하는 접근 방식은 매우 전략적입니다.

스타트업 창업자 관점에서 볼 때, 이는 제품의 기능적 확장(Feature Expansion)이 서비스의 지연 시간(Latency)이나 비용(Cost) 증가로 이어지는 문제를 해결하는 프레임워크가 될 수 있습니다. 소프트웨어 아키텍처나 AI 모델 최적화 시에도, 연산의 순차적 실행을 어떻게 병렬화하고 예측 가능한 구조로 만들 것인가가 기술적 해자(Moat)를 구축하는 핵심 요소가 될 것입니다.

댓글

아직 댓글이 없습니다. 첫 댓글을 남겨보세요.